I flip-flop (o bistabili) sono circuiti elettronici sequenziali molto semplici, utilizzati nell'elettronica digitale come dispositivi di memoria elementare. Il nome Flip-Flop deriva dal rumore che facevano i primi circuiti di questo tipo, costruiti con relè che permettevano il cambiamento di stato.

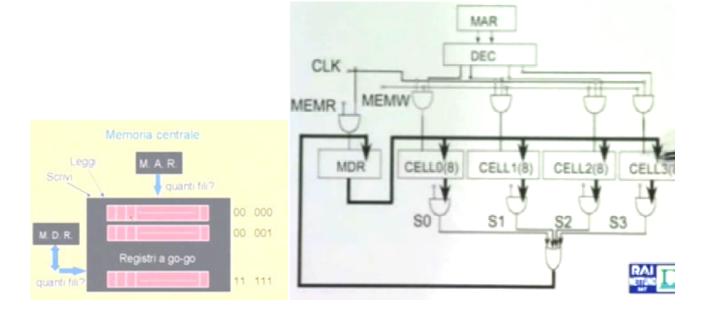

La ram dinamica è il dispositivo di memoria più usato in ambito informatico, è utilizzata in banchi come di memoria principale.

È realizzata su un chip di silicio e svolge la stessa funzione della ram statica, ma a differenza di questa, l'elemento di memoria è un semplice condensatore, anziché un flip-flop.

Ha un basso costo ed un capacità elevata, ma a differenza della ram statica, necessita di un circuito di servizio per l'operazione di rinfresco (refresh). Questa operazione è necessaria data la natura della cella di memoria che è costituita da un condensatore il quale risulta a valore logico 1 se è carico e a valore 0 se è scarico, pertanto per mantenere carichi i condensatori aventi valore 1, il circuito di refresh fornisce a intervalli di tempo costante, un impulso di corrente di ricarica.

La DRAM, acronimo di Dynamic Random Access Memory, è un tipo di RAM che immagazzina ogni bit in un diverso condensatore. Il numero di elettroni presenti nel condensatore determina se il bit è 1 o 0. Se il condensatore perde la carica, l'informazione è perduta: nel funzionamento la ricarica avviene periodicamente. Da qui la definizione di memoria dinamica, opposta alle memorie statiche come la SRAM. Per la caratteristica di perdere le informazioni in mancanza di energia, la DRAM viene definita anche volatile; è detta anche memoria solida.

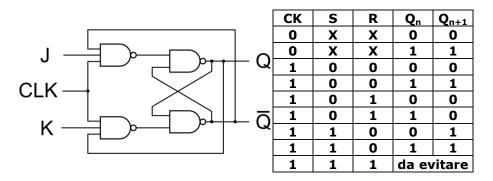

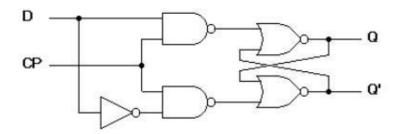

flip-flop Set Reset sincronizzato. Esso è costituito da due porte logiche NAND, dette *porte pilota*, e da altre due porte NAND che realizzano il flip-flop S R vero e proprio del tipo mostrato nella precedente fig.2.Se il clock CK è al livello logico 1 le porte pilota si comportano da NOT e quindi gli ingressi S ed R sono effettivamente coincidenti con gli omonimi ingressi del generico flip-flop Set Reset.Se, invece, il clock CK è al livello logico basso, le uscite delle due porte pilota sono al livello logico 1 indipendentemente dai valori applicati agli ingressi S e R. Per tale combinazione la "latch" a porte NAND conserva lo stato precedente e quindi il flip flop è insensibile ai comandi esterni applicati.Nella tabella della verità si riporta l'uscita futura  $Q_{n+1}$  in funzione del clock, degli ingressi S ed R e dallo stato presente  $Q_n$  (X rappresenta indifferentemente sia lo stato logico 0 che lo stato logico 1.)

Fig.4. - Flip-flop SR sincronizzato con porte NAND.

U1A e U1B costituiscono le porte pilota.

Le porte U1C e U1D rappresentano il flip-flop vero e proprio.

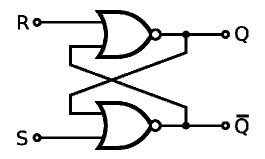

## Flip-flop SR con porte NOR

(a) Logic diagram with NAND gates